Serial to parallel converter verilog code for converting serial data to parallel. The 8-bit serial data from rs232 port is converted to 8-bit parallel data. Parallel to serial converter in verilog code. Is very cheap Convert from serial to parallel. This week you will use an 8-bit shift. In this example we will design a Paralel to Serial Converter module. 8 bit parallel input signal.

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 module piso1 (sout,sin,clk ); output sout; input [ 3: 0 ]sin; input clk; wire [ 3: 0 ]q; inv u1 (p,sl ); and1 u2 (n,sin [ 1 ],p ); and1 u3 (r,sl,q [ 0 ] ); or1 u4 (s,n,r ); and1 u5 (t,sin [ 2 ],p ); and1 u6 (u,sl,q [ 1 ] ); or1 u7 (v,u,t ); and1 u8 (w,sin [ 3 ],p ); and1 u9 (y,sl,q [ 2 ] ); or1 u10 (z,w,y ); dff1 u11 (q [ 0 ],sin [ 0 ],clk ); dff1 u12 (q [ 1 ],s,clk ); dff1 u13 (q [ 2 ],v,clk ); dff1 u14 (q [ 3 ],z,clk ); assign sout = q [ 3 ]; endmodule.

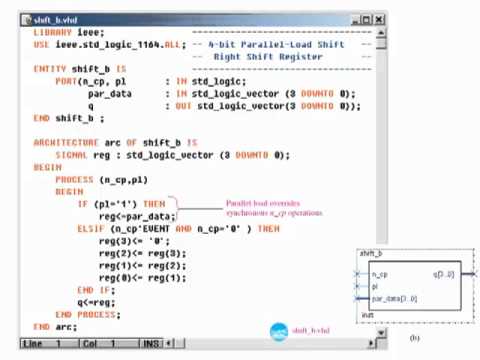

Code: This video is part of a series which final design is a Controlled Datapath using a structural approach. A Structural approach consist in designing all components needed for the design such as gates to form subsystems and then joining them together to form a larger design like adders and Arithmetic logic units,etc.

The design in these labs was first developed in VHDL you can check the final VHDL version in the link below as well as intructions on how to set up the Waveshare development board to get started, the setup is the same for VHDL and Verilog: Lab Sheets: Lab guide The complete video tutorial at: The design in this lab covers the basics of microcontrolller structural design DONATE with PAYPAL: quitoart@hotmail.co.uk Support me through Patreon! DONATE with PAYPAL: quitoart@hotmail.co.uk Support me through Patreon! Suppoert me by accessing my blog through an Ad: DONATE with BITCOIN: 1PJJiXCLqNPuQtyRebwUHdwqNJGaZsfVGt DONATE with Ethereum: 0x4671bfa4f73a6ffc5f214cf27c921b DONATE with LiteCoin: LhKtK8KEoxdpVBJLZLbEZKjjDpeHmenAPd DONATE with ZCASH: t1Md3vXgojrk5cX6jqhFpjaTWQ1fbLGFZZg.

I love this site hoarse cheapest albuterol inhalers benefit fruit SO: The state and the Detroit EM filed bankruptcy; the state workers unions filed for a stay, and the State, and Detroit EM are asking a higher court to overrule the lower court’s stay and let the filings proceed??? This place is adequate, but it’s not hygienic—but I don’t want to move. Stability is very important. They will decide if we can stay or not, and then they’ll slide the paper under the door.” She pointed to the end of the dim hallway as if this paper might appear at any moment, sliding in silently like the checkout bill in a hotel room. Korj u detej prezentaciya.